Key Technologies of HyperStreaming

Single Stream with Low Latency describes

a situation where one or two streams of information between any given device and

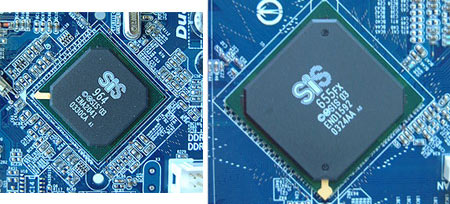

SiS's 655FX chipset have been optimized for the lowest latency between the CPU

and its I/O devices.  These situations include;

CPU-to-VGA, CPU-to-HDD, and CPU-to-Memory for example. What that means is that data will have a lower

wait state between the chipsets, and depending on exactly what the processor is

trying to communicate with, one should expect fairly dramatic increases in performance.

These situations include;

CPU-to-VGA, CPU-to-HDD, and CPU-to-Memory for example. What that means is that data will have a lower

wait state between the chipsets, and depending on exactly what the processor is

trying to communicate with, one should expect fairly dramatic increases in performance.

When it comes to multitasking, SiS has implemented a

technology called Multiple Streams with Pipelining and Concurrent

Execution.

What that means is SiS has implemented a split transaction technique

for the 655FX chipset - basically they split transactions into two

independent sub transactions, one a request, and the other a response transaction.

When other transactions can use the free EU's in between, they do, thus

increasing overall efficiency.

The example above is intended to illustrate that

four independent request/respond transactions can be computed while a

conventional system would only be able to finish two.

To help keep things moving at a quick speed, SiS place six

request/response channels (three for each) between the 655FX Northbridge and the

964 Southbridge. That is a total of 1.2GB/s of bandwidth between the two

core logic chipsets. With traditional chipsets, there's only two channels (one

upstream and one downstream) and all data, no matter how trivial, is treated as

equal and passed through with the same priority.

With HyperStreaming, not only is the data being computed in

parallel, certain data streams receive higher priority, and

are thus worked on first and have more channels between the bridges.

For instance, HDD performance of the SiS964 is the highest we have ever

seen thanks to the fact

that hard drive streams have their own independent channels to the

Northbridge.

|